Figure 11.56

1. Pendahuluan [kembali]

Secara umum, presettable counter bekerja berdasarkan sinyal clock dan sinyal kontrol seperti load atau preset enable, yang memungkinkan pengguna mengatur nilai awal penghitung. Teknologi ini banyak diterapkan dalam sistem digital berbasis rangkaian logika, mikrokontroler, maupun dalam desain sistem berbasis FPGA

2. Tujuan [kembali]

- Mengetahui dan memahami materi tentang presettable four bit counters

- Menyelesaikan tugas mata kuliah sistem digital

3. Alat dan Bahan [kembali]

1. Gerbang NOT

Gerbang NOT merupakan suatu jenis logic gates yang memiliki fungsi sebagai suatu pembalik, atau yang dikenal dengan istilah inverter. Dengan demikian, nilai yang merupakan hasil keluaran (output) yang didapatkan akan selalu bertolak belakang dengan input..

2. Gerbang NAND (Not AND)

Gerbang NAND adalah salah satu gerbang logika dasar dalam elektronika digital yang menghasilkan output yang bernilai kebalikan dari output gerbang AND. Artinya, output dari gerbang NAND akan bernilai rendah (0) hanya jika semua inputnya bernilai tinggi (1). Jika ada satu atau lebih input yang bernilai rendah, maka outputnya akan bernilai tinggi.

IC 74154 adalah sebuah dekoder/demultiplekser 4-ke-16 saluran, yang berarti perangkat ini dapat mengambil input 4-bit dan menghasilkan satu dari 16 output aktif rendah. IC ini sering digunakan dalam aplikasi yang memerlukan pemilihan satu dari banyak jalur, seperti dalam memori atau pengendalian perangkat.

5. Counter

Counter dalam sistem digital adalah rangkaian logika yang digunakan untuk menghitung jumlah pulsa atau sinyal. Biasanya digunakan untuk mengukkur waktu, menghasilkan frekuensi, atau menghitung peristiwa dalam berbagai aplikasi elektronik dan komputer.

4. Dasar Teori [kembali]

11.11.3 Design Procedure

Counter dengan Urutan Arbitrer (Arbitrary Sequence Counter)

Pada gambar Figure 11.27, ditunjukkan sebuah rangkaian counter (pencacah) yang menggunakan tiga buah JK flip-flop dan beberapa gerbang logika (AND, OR, NOT) untuk mengatur urutan pencacahan yang tidak mengikuti pola biner standar. Rangkaian ini dirancang untuk menghasilkan urutan bilangan biner khusus sesuai kebutuhan aplikasi tertentu, sehingga disebut sebagai arbitrary sequence counter atau counter dengan urutan arbitrer.

Struktur Rangkaian

Rangkaian terdiri atas tiga buah flip-flop JK yang dinamai:

FF-A: menyimpan bit A,

FF-B: menyimpan bit B,

FF-C: menyimpan bit C.

Ketiga flip-flop dikendalikan oleh clock yang sama (clock-in) sehingga bekerja secara sinkron. Input J dan K dari setiap flip-flop tidak dihubungkan langsung ke logika 1, tetapi dikendalikan oleh gerbang logika kombinasi yang menghitung input berdasarkan kondisi saat ini (nilai A, B, dan C).

Fungsi Logika J dan K

Berikut adalah persamaan logika untuk masing-masing input JK flip-flop:

FF-A:

FF-B:

FF-C:

Fungsi-fungsi logika ini dirancang agar flip-flop hanya toggle (berubah kondisi) saat kondisi tertentu terpenuhi. Dengan kata lain, perubahan pada setiap bit A, B, atau C akan dikendalikan oleh logika kombinasi berdasarkan keadaan bit-bit lainnya.

Prinsip Kerja

Pada setiap pulsa clock:

Nilai J dan K untuk masing-masing flip-flop dihitung berdasarkan nilai A, B, dan C saat ini.

Jika dan , flip-flop akan toggle (berubah dari 0 ke 1 atau sebaliknya).

Jika dan , flip-flop akan reset ke 0.

Jika dan , flip-flop akan set ke 1.

Jika dan , tidak ada perubahan.

Dengan logika seperti ini, urutan keadaan counter tidak lagi 000 → 001 → 010 → 011 → ..., tetapi akan mengikuti pola yang ditentukan oleh fungsi logika di atas. Misalnya, bisa jadi urutannya adalah 000 → 001 → 011 → 110 → dst.

11.8 Example 11.8

Flip-flop digunakan secara luas dalam sistem digital sebagai elemen memori, register, dan counter, serta untuk menyinkronkan sinyal input dengan sinyal clock. Ada beberapa jenis flip-flop yang umum digunakan, antara lain SR (Set-Reset), JK, D (Data), dan T (Toggle), yang masing-masing memiliki karakteristik dan aplikasi khusus. Misalnya, flip-flop JK mengatasi kelemahan flip-flop SR dengan menghilangkan kondisi terlarang dan memungkinkan fungsi toggle. Flip-flop juga dapat dikendalikan oleh sinyal clock sehingga perubahan output hanya terjadi pada saat sinyal clock aktif, sehingga cocok untuk aplikasi sinkron.

Gambar D FF (a) simbol, (b) rangkaian ekivalennya dan (c) tabel kebenaran

Counter adalah rangkaian logika sekuensial yang digunakan untuk menghitung jumlah pulsa input. Counter terbagi dua jenis:

Asynchronous (Ripple Counter): setiap flip-flop dipicu oleh output flip-flop sebelumnya.

Synchronous Counter: semua flip-flop dipicu oleh clock yang sama secara bersamaan.

JK Flip-Flop adalah jenis flip-flop yang umum digunakan dalam perancangan counter karena fleksibel:

Ketika J = K = 1, maka output akan toggle (berubah keadaan).

Flip-flop akan berubah hanya pada sisi naik/turun dari clock tergantung jenisnya.

Untuk membentuk urutan pencacahan tertentu, digunakan fungsi logika eksitasi yang mengatur kapan masing-masing flip-flop akan toggle. Hal ini dilakukan dengan bantuan gerbang AND, OR, dan NOT yang menyusun kondisi input J dan K dari masing-masing flip-flop berdasarkan output-output lainnya.

1. Sebuah D Flip-Flop menerima input D = 1 dan pulsa clock aktif (rising edge). Tentukan output Q setelah clock aktif.

Jawaban:

Pada saat clock aktif, output Q akan mengikuti nilai input D. Karena D = 1, maka Q menjadi 1.

2. Jika sebuah D Flip-Flop memiliki output Q = 0 dan input D berubah menjadi 1, tetapi clock belum aktif, bagaimana kondisi output Q?

Jawaban:

Output Q tidak berubah sebelum clock aktif, jadi tetap Q = 0 sampai clock menerima pulsa aktif.

1. Jelaskan mengapa D Flip-Flop disebut sebagai "data latch" dan bagaimana fungsinya dalam menyimpan data.

Jawaban:

D Flip-Flop disebut data latch karena hanya menyimpan nilai data input D pada saat sinyal clock aktif. Ini memungkinkan data disimpan secara stabil sampai clock berikutnya, sehingga D Flip-Flop berfungsi sebagai memori satu bit yang menyimpan data secara sinkron.

2. Apa yang terjadi jika input D Flip-Flop berubah saat clock tidak aktif? Bagaimana hal ini mempengaruhi output?

Jawaban:

Jika input D berubah saat clock tidak aktif, output Q tidak akan berubah karena D Flip-Flop hanya memperbarui output pada saat tepi aktif clock. Ini menjaga kestabilan data yang tersimpan sampai clock berikutnya.

11.15 Application-Relevant Information

1. Deskripsi Rangkaian

Problem 7 menampilkan sebuah rangkaian pencacah (counter) yang terdiri dari tiga buah JK Flip-Flop (dilabeli sebagai A, B, dan C) yang dirangkai secara berantai (ripple). Rangkaian ini menggunakan logika tambahan berupa gerbang AND untuk mendeteksi kondisi tertentu dan melakukan reset otomatis terhadap seluruh flip-flop.

2. Prinsip Kerja Flip-Flop JK

Setiap flip-flop pada rangkaian bekerja dalam mode toggle, karena seluruh input J = 1 dan K = 1. Dengan demikian, flip-flop akan mengubah keadaan (0 → 1 atau 1 → 0) setiap kali menerima sinyal clock pada inputnya.

3. Aliran Clock

Flip-Flop A menerima clock langsung dari sumber osilator (frekuensi 600 kHz).

Flip-Flop B menerima clock dari output Q̅ Flip-Flop A.

Flip-Flop C menerima clock dari output Q̅ Flip-Flop B.

Hal ini menunjukkan bahwa ketiga flip-flop bekerja dalam ripple configuration (asynchronous counter).

4. Sistem Reset Otomatis

Output dari flip-flop A (Q_A) dan flip-flop B (Q_B) dihubungkan ke sebuah gerbang AND. Output dari gerbang AND digunakan untuk mengaktifkan Clear (CLR) pada semua flip-flop.

Artinya, jika A = 1 dan B = 1, maka hasil AND = 1 → yang membuat output Clear aktif (logika rendah) → semua flip-flop direset ke kondisi awal (000).

5. Analisis Urutan Hitungan

Karena counter di-reset secara otomatis saat mencapai kondisi biner 011 (A = 1, B = 1), maka hanya ada tiga keadaan yang aktif, yaitu:

Dengan demikian, rangkaian ini menjadi sebuah counter dengan modulus 3 (mod-3 counter).

6. Jawaban yang Diminta dalam Soal

✅ a. Modulus Counter

Karena hanya 3 keadaan yang digunakan (000, 001, 010), maka:

✅ b. Frekuensi Output B

Clock input = 600 kHz

Karena hanya 3 kondisi yang dilewati, maka:

✅ c. Duty Cycle Output C

Flip-Flop C (output C) tidak pernah mencapai kondisi untuk toggle karena counter di-reset sebelum itu terjadi.

Maka:

7. Simulasi Proteus

Rangkaian yang dibuat di Proteus menggunakan IC 7476 (JK Flip-Flop) dan satu gerbang NAND untuk mendeteksi kondisi A = 1 dan B = 1. Clock generator digunakan sebagai sumber sinyal berfrekuensi 600 kHz. Hasil simulasi menunjukkan bahwa:

Output B berosilasi dengan frekuensi 200 kHz.

Output C tetap berada di logika rendah.

Counter terus mengulang dari 000 → 001 → 010 → reset.

1. Sebuah rangkaian counter terdiri dari 3 JK Flip-Flop yang disusun seperti pada Problem 7. Flip-flop akan reset otomatis ketika Q_A = 1 dan Q_B = 1. Clock utama yang masuk ke FF-A adalah 1 MHz.

Tentukan:

a) Modulus counter

b) Frekuensi output flip-flop B (Q_B)

c) Frekuensi output flip-flop A (Q_A)

Jawaban:

a) Modulus counter

Seperti pada Problem 7, rangkaian akan menghitung:

Jumlah state aktif = 3, maka:

5. Percobaan [kembali]

a) Prosedur[kembali]

Siapkan komponen pada simulator digital seperti Proteus:

-

3 buah JK Flip-Flop (IC 7476 atau 74LS73)

-

Gerbang logika AND dan OR (IC 7408 dan 7432)

-

Sumber clock (pulser atau generator gelombang persegi)

-

LED atau display 7-segmen (opsional) untuk menampilkan output

-

-

Hubungkan semua flip-flop dengan sumber clock yang sama (sinkron).

-

Rancang logika input J dan K untuk masing-masing flip-flop menggunakan kombinasi logika dari output flip-flop lain sesuai diagram.

-

Hubungkan output Q dari masing-masing flip-flop sebagai bit-bit output counter (A, B, C).

-

Lakukan simulasi dan amati perubahan output setiap kali clock aktif.

-

Periksa apakah urutan pencacahan sesuai dengan yang diinginkan (0→1→2→... atau urutan khusus).

b) Rangkaian simulasi [kembali]

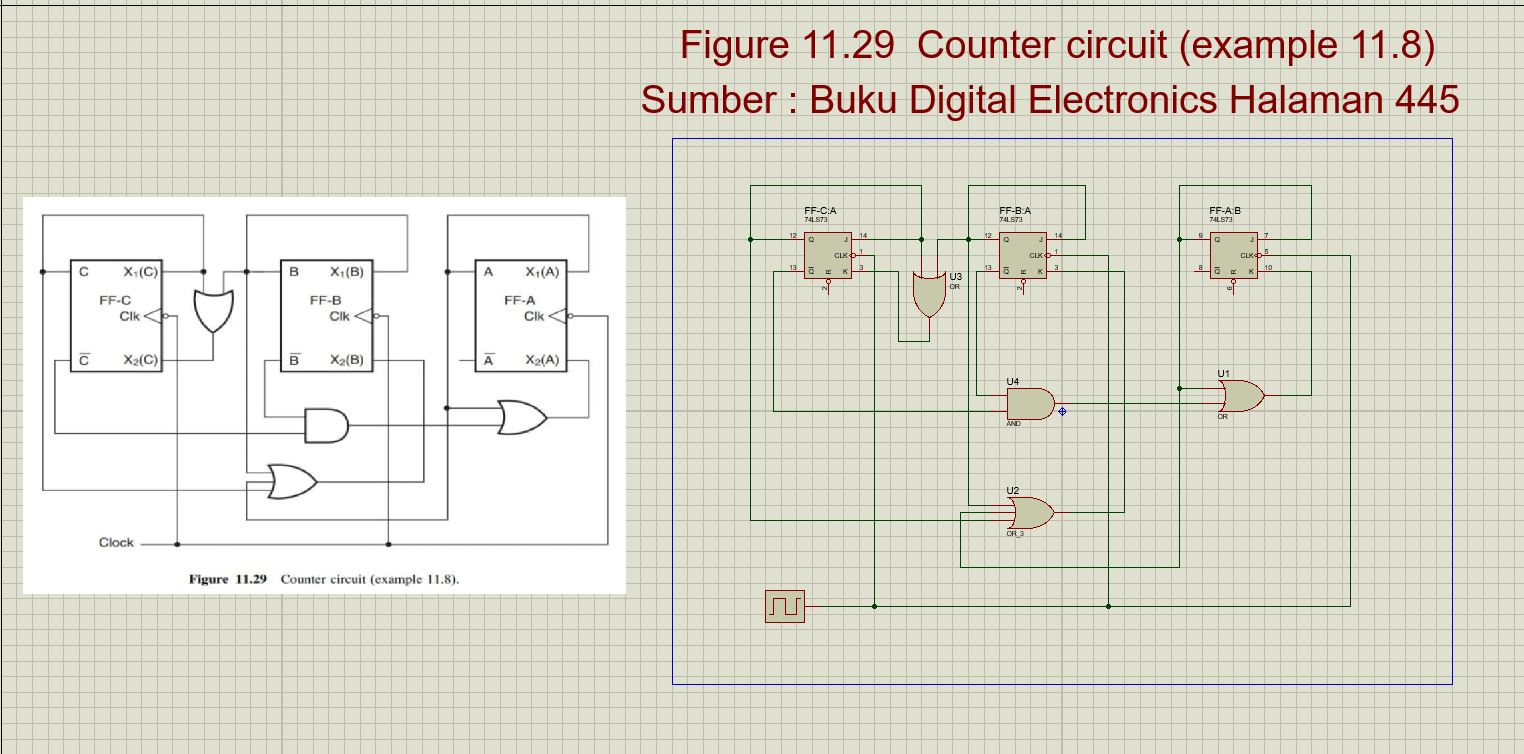

Rangkaian pada Gambar 11.29 menggunakan 3 buah JK Flip-Flop (FF-A, FF-B, FF-C) yang disusun secara sinkron karena semuanya terhubung ke clock yang sama. Namun, masing-masing flip-flop akan berubah kondisi hanya jika syarat tertentu dari input logikanya terpenuhi.

-

Flip-Flop A: selalu toggle setiap ada pulsa clock (J = K = 1).

-

Flip-Flop B: hanya toggle jika kondisi tertentu terpenuhi, misalnya ketika A = 1.

-

Flip-Flop C: hanya toggle jika kombinasi dari A dan B memenuhi persyaratan logika, seperti A·B = 1 atau fungsi lainnya tergantung rancangan logika.

Logika OR dan AND digunakan untuk menghasilkan sinyal eksitasi untuk masing-masing flip-flop berdasarkan keadaan output sebelumnya. Dengan konfigurasi ini, counter dapat menghitung dalam urutan biner tertentu seperti modulo-N counter (misal mod-6, mod-8).

- Contoh 1:

Sebuah D Flip-Flop menerima input D = 1 dan pulsa clock aktif (rising edge). Tentukan output Q setelah clock aktif.

Jawaban:

Pada saat clock aktif, output Q akan mengikuti nilai input D. Karena D = 1, maka Q menjadi 1. - Contoh 2:

Jika sebuah D Flip-Flop memiliki output Q = 0 dan input D berubah menjadi 1, tetapi clock belum aktif, bagaimana kondisi output Q?

Jawaban:

Output Q tidak berubah sebelum clock aktif, jadi tetap Q = 0 sampai clock menerima pulsa aktif.

- Problem 1:

Jelaskan mengapa D Flip-Flop disebut sebagai "data latch" dan bagaimana fungsinya dalam menyimpan data.

Jawaban:

D Flip-Flop disebut data latch karena hanya menyimpan nilai data input D pada saat sinyal clock aktif. Ini memungkinkan data disimpan secara stabil sampai clock berikutnya, sehingga D Flip-Flop berfungsi sebagai memori satu bit yang menyimpan data secara sinkron. - Problem 2:

Apa yang terjadi jika input D Flip-Flop berubah saat clock tidak aktif? Bagaimana hal ini mempengaruhi output?

Jawaban:

Jika input D berubah saat clock tidak aktif, output Q tidak akan berubah karena D Flip-Flop hanya memperbarui output pada saat tepi aktif clock. Ini menjaga kestabilan data yang tersimpan sampai clock berikutnya.

- Soal 1:

Pada D Flip-Flop, kapan output Q akan mengikuti nilai input D?

a. Setiap saat input D berubah

b. Saat clock aktif (rising edge)

c. Saat clock tidak aktif

d. Saat reset aktif

e. Saat preset aktif

Jawaban: b - Soal 2:

Berapa banyak input yang dimiliki oleh D Flip-Flop?

a. 1 input dan 1 output

b. 2 input dan 1 output

c. 1 input dan 2 output

d. 2 input dan 2 output

e. 3 input dan 2 output

Jawaban: d

(Input: D dan Clock; Output: Q dan Q̅)

c) Video Simulasi [kembali]

6. Download File [kembali]

- Download Rangkaian disini

- Download rangkaian 11.56 klik disini

- Download rangkaian 11.27 klik disini

- Download Video Rangkaian disini

- Download Datasheet And Gate klik disini

- Download Datasheet Or Gate klik disini

- Download Datasheet Nor Gate klik disini

- Download HTML disini

Komentar

Posting Komentar