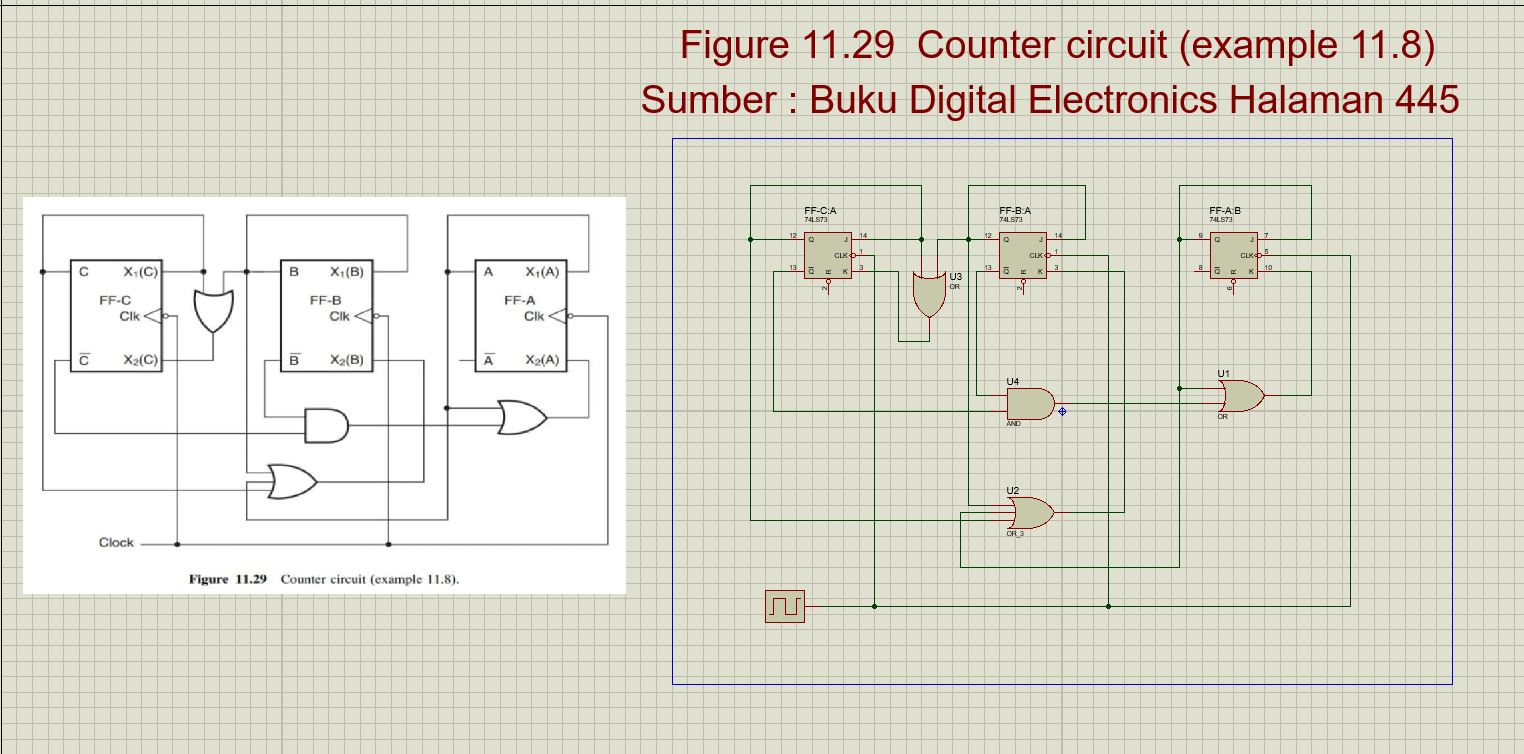

Figure 11.29

1. Pendahuluan [kembali]

2. Tujuan [kembali]

- Mempelajari implementasi dan prinsip kerja rangkaian counter sinkron.

- Mengidentifikasi fungsi masing-masing flip-flop dan gerbang logika dalam menyusun urutan pencacahan.

- Menganalisis sinyal keluaran counter terhadap pulsa clock masukan.

- Membangun rangkaian counter berdasarkan gambar skematik dengan benar.

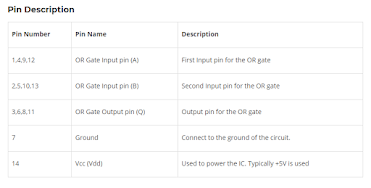

3. Alat dan Bahan [kembali]

- IC ini berisi 2 buah JK flip-flop.

- Output flip-flop akan berubah hanya saat tepi turun (falling edge) dari sinyal clock.

- Ketika J = K = 1, maka flip-flop akan toggle (berubah ke keadaan berlawanan).

- Pin Clear dapat digunakan untuk mengatur ulang output ke 0 tanpa menunggu clock.

Fungsi utama: digunakan untuk menyimpan 1 bit data, membentuk counter, register, pembagi frekuensi, dll.

4. Dasar Teori [kembali]

Flip-flop digunakan secara luas dalam sistem digital sebagai elemen memori, register, dan counter, serta untuk menyinkronkan sinyal input dengan sinyal clock. Ada beberapa jenis flip-flop yang umum digunakan, antara lain SR (Set-Reset), JK, D (Data), dan T (Toggle), yang masing-masing memiliki karakteristik dan aplikasi khusus. Misalnya, flip-flop JK mengatasi kelemahan flip-flop SR dengan menghilangkan kondisi terlarang dan memungkinkan fungsi toggle. Flip-flop juga dapat dikendalikan oleh sinyal clock sehingga perubahan output hanya terjadi pada saat sinyal clock aktif, sehingga cocok untuk aplikasi sinkron.

Counter adalah rangkaian logika sekuensial yang digunakan untuk menghitung jumlah pulsa input. Counter terbagi dua jenis:

-

Asynchronous (Ripple Counter): setiap flip-flop dipicu oleh output flip-flop sebelumnya.

-

Synchronous Counter: semua flip-flop dipicu oleh clock yang sama secara bersamaan.

JK Flip-Flop adalah jenis flip-flop yang umum digunakan dalam perancangan counter karena fleksibel:

-

Ketika J = K = 1, maka output akan toggle (berubah keadaan).

-

Flip-flop akan berubah hanya pada sisi naik/turun dari clock tergantung jenisnya.

Untuk membentuk urutan pencacahan tertentu, digunakan fungsi logika eksitasi yang mengatur kapan masing-masing flip-flop akan toggle. Hal ini dilakukan dengan bantuan gerbang AND, OR, dan NOT yang menyusun kondisi input J dan K dari masing-masing flip-flop berdasarkan output-output lainnya.

5. Percobaan [kembali]

a) Prosedur[kembali]

Siapkan komponen pada simulator digital seperti Proteus:

-

3 buah JK Flip-Flop (IC 7476 atau 74LS73)

-

Gerbang logika AND dan OR (IC 7408 dan 7432)

-

Sumber clock (pulser atau generator gelombang persegi)

-

LED atau display 7-segmen (opsional) untuk menampilkan output

-

-

Hubungkan semua flip-flop dengan sumber clock yang sama (sinkron).

-

Rancang logika input J dan K untuk masing-masing flip-flop menggunakan kombinasi logika dari output flip-flop lain sesuai diagram.

-

Hubungkan output Q dari masing-masing flip-flop sebagai bit-bit output counter (A, B, C).

-

Lakukan simulasi dan amati perubahan output setiap kali clock aktif.

-

Periksa apakah urutan pencacahan sesuai dengan yang diinginkan (0→1→2→... atau urutan khusus).

b) Rangkaian simulasi [kembali]

Rangkaian pada Gambar 11.29 menggunakan 3 buah JK Flip-Flop (FF-A, FF-B, FF-C) yang disusun secara sinkron karena semuanya terhubung ke clock yang sama. Namun, masing-masing flip-flop akan berubah kondisi hanya jika syarat tertentu dari input logikanya terpenuhi.

-

Flip-Flop A: selalu toggle setiap ada pulsa clock (J = K = 1).

-

Flip-Flop B: hanya toggle jika kondisi tertentu terpenuhi, misalnya ketika A = 1.

-

Flip-Flop C: hanya toggle jika kombinasi dari A dan B memenuhi persyaratan logika, seperti A·B = 1 atau fungsi lainnya tergantung rancangan logika.

Logika OR dan AND digunakan untuk menghasilkan sinyal eksitasi untuk masing-masing flip-flop berdasarkan keadaan output sebelumnya. Dengan konfigurasi ini, counter dapat menghitung dalam urutan biner tertentu seperti modulo-N counter (misal mod-6, mod-8).

a. Example

- Contoh 1:

Sebuah D Flip-Flop menerima input D = 1 dan pulsa clock aktif (rising edge). Tentukan output Q setelah clock aktif.

Jawaban:

Pada saat clock aktif, output Q akan mengikuti nilai input D. Karena D = 1, maka Q menjadi 1. - Contoh 2:

Jika sebuah D Flip-Flop memiliki output Q = 0 dan input D berubah menjadi 1, tetapi clock belum aktif, bagaimana kondisi output Q?

Jawaban:

Output Q tidak berubah sebelum clock aktif, jadi tetap Q = 0 sampai clock menerima pulsa aktif.

- Problem 1:

Jelaskan mengapa D Flip-Flop disebut sebagai "data latch" dan bagaimana fungsinya dalam menyimpan data.

Jawaban:

D Flip-Flop disebut data latch karena hanya menyimpan nilai data input D pada saat sinyal clock aktif. Ini memungkinkan data disimpan secara stabil sampai clock berikutnya, sehingga D Flip-Flop berfungsi sebagai memori satu bit yang menyimpan data secara sinkron. - Problem 2:

Apa yang terjadi jika input D Flip-Flop berubah saat clock tidak aktif? Bagaimana hal ini mempengaruhi output?

Jawaban:

Jika input D berubah saat clock tidak aktif, output Q tidak akan berubah karena D Flip-Flop hanya memperbarui output pada saat tepi aktif clock. Ini menjaga kestabilan data yang tersimpan sampai clock berikutnya.

- Soal 1:

Pada D Flip-Flop, kapan output Q akan mengikuti nilai input D?

a. Setiap saat input D berubah

b. Saat clock aktif (rising edge)

c. Saat clock tidak aktif

d. Saat reset aktif

e. Saat preset aktif

Jawaban: b - Soal 2:

Berapa banyak input yang dimiliki oleh D Flip-Flop?

a. 1 input dan 1 output

b. 2 input dan 1 output

c. 1 input dan 2 output

d. 2 input dan 2 output

e. 3 input dan 2 output

Jawaban: d

(Input: D dan Clock; Output: Q dan Q̅)

c) Video Simulasi [kembali]

6. Download File [kembali]

- Download Rangkaian disini

- Download Video Rangkaian disini

- Download Datasheet And Gate klik disini

- Download Datasheet Or Gate klik disini

- Download Datasheet Nor Gate klik disini

- Download HTML disini

Komentar

Posting Komentar